|

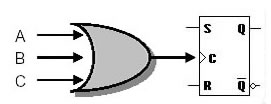

In queste reti non esiste nessun clock, si elimina quindi l'ipotesi di un segnale di sincronismo generale (tipico delle reti sincrone), e si progetta una rete che cambia stato in conseguenza di un impulso su uno qualsiasi degli ingressi. Le ipotesi di corretto funzionamento richiedono che si verifichi in ingresso un solo impulso alla volta, e che la durata dell'impulso sia sufficiente a consentire alla rete di assestarsi. Questo tipo di reti prevedono un segnale di pseudo-sincronismo ottenuto come OR degli ingressi, si genera cosi un impulso di sincronismo in corrispondenza di un qualsiasi impulso di ingresso. Supponendo di avere tre ingressi A,B,C, il clock sarà:

Un clock di questo tipo × chiamato Imput Driven (guidato dagli eventi).

Tutto quanto riportato in questa pagina × a puro scopo informativo personale. Se non ti trovi in accordo con quanto riportato nella pagina, vuoi fare delle precisazioni, vuoi fare delle aggiunte o hai delle proposte e dei consigli da dare, puoi farlo mandando un email. Ogni indicazione × fondamentale per la continua crescita del sito.